-

UAV Products

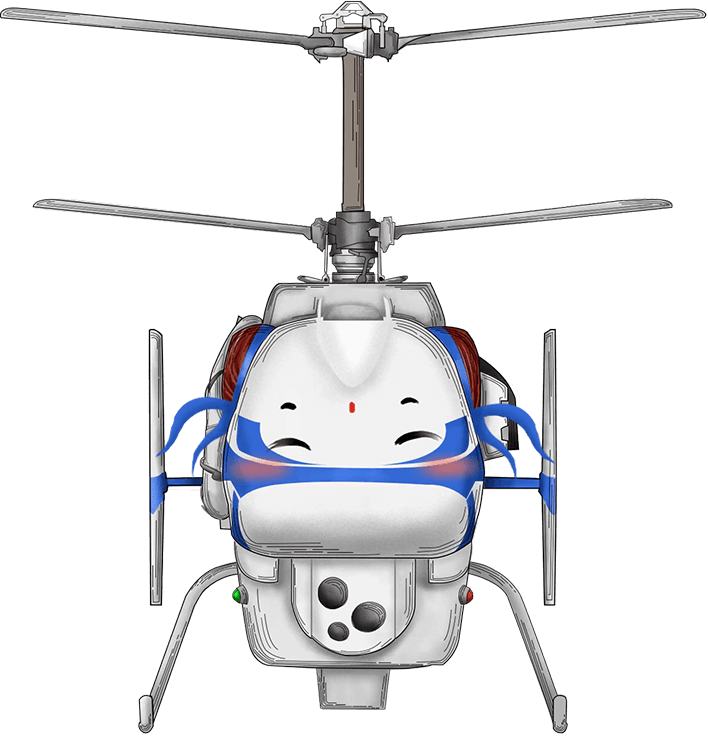

- TD550 Coaxial Unmanned Helicopter

- Lanying R6000 Tiltrotor Aircraft

- TD220 Coaxial Unmanned Helicopter

- Leiying Q20 Quadrotor Flight Platform

- Q100 Agricultural UAV

- Boying T1400 Tandem Unmanned Helicopter

- Design Techniques for Modification from Manned Helicopter to Unmanned Helicopter

- TA-Q3 Pipeline Patrol Mini UAV

- TA-Q4 Warehouse Patrol Mini UAV

- TA-Q5 Tunnel Patrol UAV

-

Ground Equipment

-

Airborne Equipment

- Multiple Redundant Flight Control Computer

- Dual-Redundancy Servo Controller

- 270V Dual-Redundancy Actuator Servo System

- Smart Actuator

- Dual-Redundancy Electric Servo Actuator(Rotary Actuator)

- Dual-Redundancy Electric Servo Actuator(Linear Actuator)

- 28V Actuator Servo Driver

- Unmanned Helicopter Integrated Tester

-

Rotor Blades

-

Composite Products

-

Logistic Transportation

-

Public Security Law Enforcement

-

Border and Coast Security Guard

-

Powerline Inspection and Construction

-

Oil and Gas Industry